次世代抗電漿蝕刻技術—Y Coating

一、前言

目前影響晶圓良率的關鍵因素之一是蝕刻設備的內部零件防護。這些零件長期暴露於高能電漿環境中,極易受到蝕刻與腐蝕侵害。一旦塗層失效產生剝落,將可能釋出微粒與粉塵,直接污染晶圓,導致製程缺陷與良率下降。尤其隨著先進製程線寬不斷微縮,晶圓對微粒污染的容忍度越來越低,製程穩定性面臨更大挑戰。面對此一趨勢,發展具備高度抗電漿腐蝕能力的次世代塗層技術,已成為提升半導體製程可靠度的關鍵所在。

二、當前業界使用的技術及其弊端

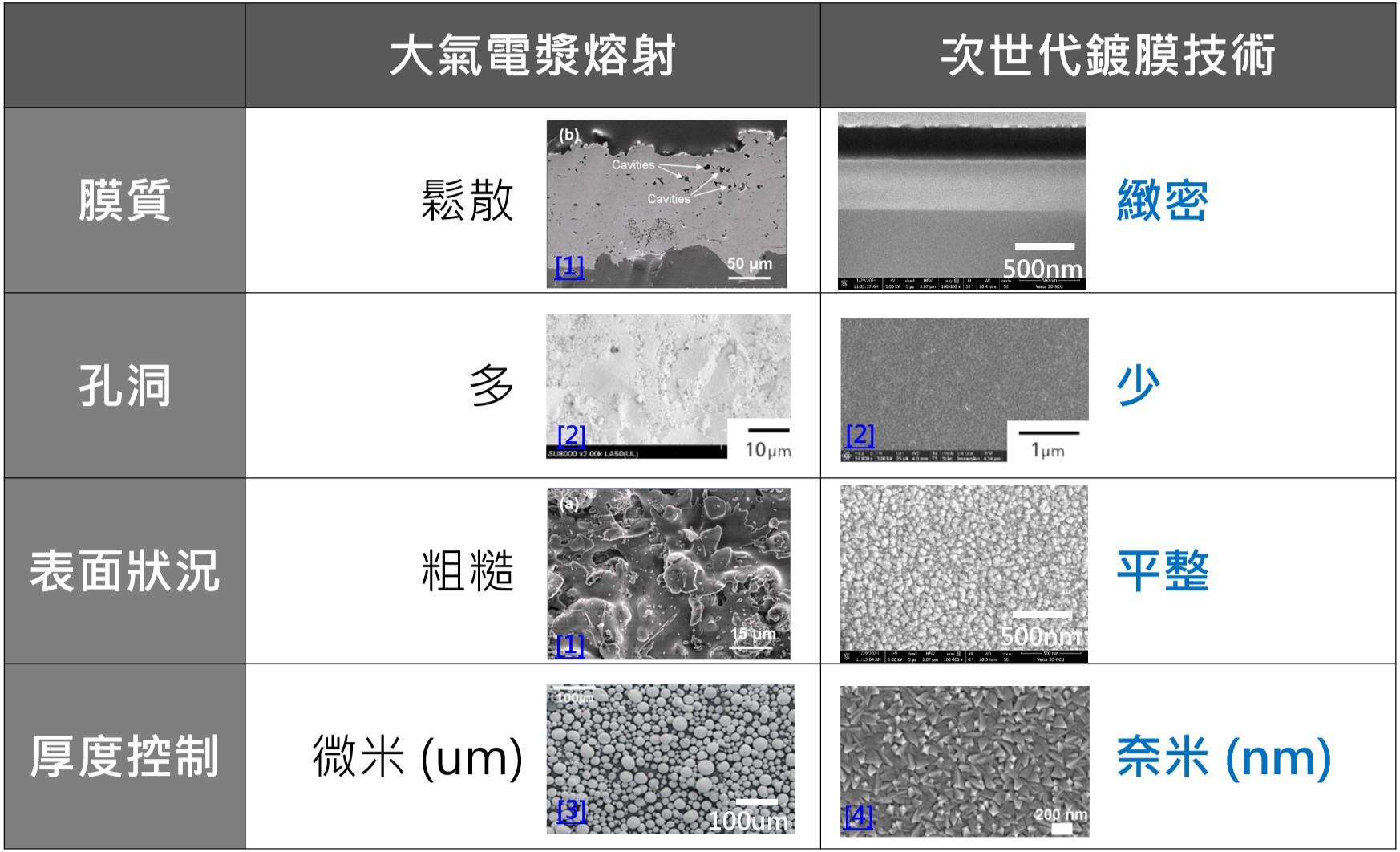

目前業界主流技術採用大氣電漿熔射(APS)技術,以釔化合物(Y-Coating)在基材表面形成抗電漿蝕刻保護膜。APS具備低溫環境下以相對簡單便宜的成本來達到抗腐蝕的目的,但鍍層表面結構易產生孔隙,成為氟離子滲透與侵蝕的通道,進而影響塗層壽命與製程穩定性。此技術雖曾在五年前被廣泛應用,但隨著線寬持續微縮,APS 已難以滿足現今製程對膜層緻密性與微粒控制的高要求。

大永真空推出次世代抗電漿蝕刻塗層技術,以高緻密、高附著、高純度鍍層,打造更穩定且長效的鍍膜解決方案,迎戰先進製程挑戰。

三、次世代抗電漿蝕刻技術

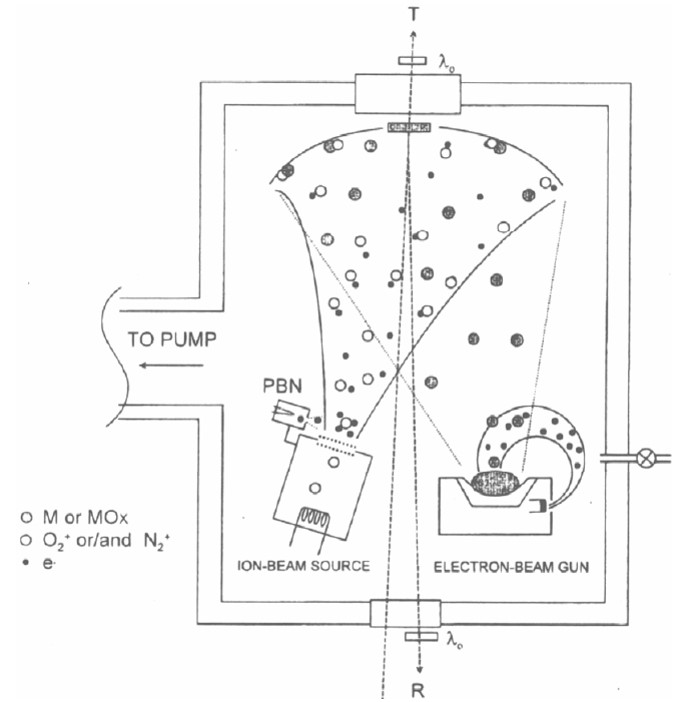

物理氣相沉積(PVD)技術,是將固態材料氣化為氣態後沉積於基材表面,再凝結為固態薄膜,以達成鍍膜效果。而離子輔助電子束蒸鍍(IAD)則在此基礎上導入高動能離子輔助,藉由質量大、動能高的離子撞擊效應,促使膜層在沉積過程中形成更緻密、有序、純度更高的結構。

相較於傳統的大氣電漿熔射(APS)技術,IAD 所沉積的膜層具有更小的孔隙率、更高的平整度與奈米級厚度控制能力,能在不犧牲鍍膜品質的前提下應用於線寬日益縮小的半導體關鍵零組件。此技術不僅適用於微結構的高精密鍍膜需求,更克服了 APS 僅能應用於大尺度基材的限制,為次世代抗電漿蝕刻薄膜提供全新解方。

四、結論

在大氣電漿熔射(APS)技術逐漸難以滿足現代製程需求的今日,產業迫切需要更先進、精密的抗電漿蝕刻鍍膜技術。大永真空堅信,離子輔助電子槍蒸鍍(IAD)正是次世代的最佳解方。

IAD 可大幅改善 APS 所面臨的膜層結構粗糙與孔隙過大等問題,所形成的膜層緻密且完整,有效阻絕氟離子穿透晶界或孔隙所造成的腐蝕與脫膜風險。同時,IAD 可精準控制膜層厚度至奈米級別,完美對應現今日益微縮的線寬與線距設計需求。

選擇大永真空的次世代抗蝕鍍膜技術,讓耐久、穩定的蝕刻零件不再是奢望,有效提升良率與製程穩定性,是您邁向高可靠性製程的關鍵一步。